EENG 426/CPSC 459/ENAS 876 Fall 2018: Final Projects

EENG 426/CPSC 459/ENAS 876 catalog entry. An upper-level course on compiling computations into digital circuits using asynchronous design techniques. Emphasis is placed on the synthesis of circuits that are robust to uncertainties in gate and wire delays by the process of program transformations. Topics include circuits as concurrent programs, delay-insensitive design techniques, synthesis of circuits from programs, timing analysis and performance optimization, pipelining, and case studies of complex asynchronous designs.

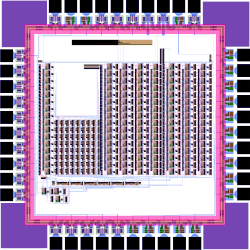

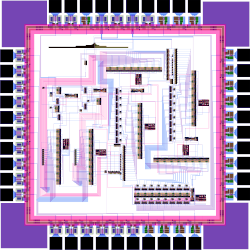

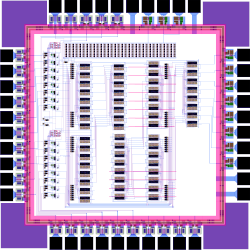

EENG 426/CPSC 459/ENAS 876 is Yale's introductory asynchronous VLSI course. Students learn about digital VLSI, and get to tape-out a full-custom chip of their choosing at the end of the semester using the MOSIS VLSI service.

Design style. The circuits were implemented with a combination of QDI and bundled data logic. All control is QDI, and large datapath elements were bundled data.

Tools. The main tools used by the students were the following:

magic, for full-custom layout. We also provided scripts to automate the layout of groups of transistors.irsim, for digital switch-level simulation. This was locally hacked to provide some extra functionality.- The

ACTtools for asynchronous designaflat, to generate the flat production rules for the designlvp, to compare layout versus production rulesprs2sim, to create sim/al files from production rulesprsim, a digital production-rule simulator

lab3, sample CHP to production rule generator (also the lab3 assignment, hence the name)Xyce, for analog simulation.ext2sp, locally modified to generate hierarchical spice netlistlabelplugsandwellcheck, for well-plug checking

Projects

|

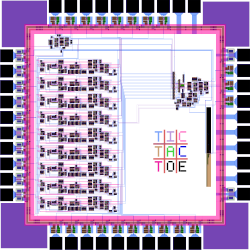

Tic Tac Toe |

|

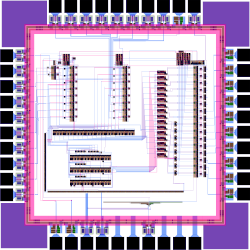

Calculator |

|

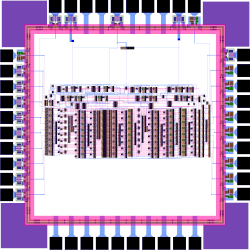

Sparse vector compress/decompress |

|

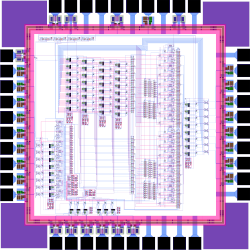

Microcontroller |

|

Dot product engine |

|

Scrambler/descrambler |

|

Matrix multiplication |