| [4/2025] | Rajit participated in a CRA meeting on brain-computer interfaces. |  |

| [4/2025] | Rajit participated in a Royal Society discussion meeting on Bits, neurons, and qubits for sustainable AI. Thanks to Osvaldo Simeone, Bipin Rajendran, and Olga Kazakova for organizing this event. |  |

| [3/2025] | Three regular track papers from the group accepted to the IEEE ASYNC symposium!- Prafull's paper is on data readout in an event-based imager.

- Karthi's paper is on automated decomposition of CHP programs.

- Xiayuan and Rui's paper is on handling repeated channel actions during dataflow synthesis of CHP programs.

|  |

| [3/2025] | Rui's paper on an asynchronous high-level synthesis (HLS) engine with pipelined resource sharing accepted to DAC. |  |

| [3/2025] | Ruslan's paper on emulating hybrid CHP + PRS asynchronous circuits integrated with synchronous environments on FPGAs is accepted to IEEE TCAD. |

| [1/2025] | Rajit participated in the inaugural Bangalore Neuromorphic Engineering Workshop. The workshop, hosted by the Indian Institute of Science, is modeled on Telluride and Capo Caccia, and is meant to serve the Asia-Pacific region. |

| [7/2024] | Videos from the 2024 summer school on asynchronous design are now available. |

| [6/2024] | Rajit presented an overview of the ACT tools at the Free Silicon Conference in Paris. |

| [5/2024] | Rajit presented an overview of neuromorphic computing and its relation to neuro-symbolic systems at the first conference on neuro-symbolic systems held at Berkeley. Photograph courtesy J. Roychowdhury. |  |

| [3/2024] |

Our group participated in Computer Architecture Day hosted by NYU. The Yale contingent included students from our group as well as Prof. Bhattacharjee's group.

|

| [3/2024] | Congratulations to Ruslan, headed to his first job! |

| [2/2024] | Our ISCA paper with Profs. Bhattacharjee and Khandelwal's groups on a networked brain-computer interface design is selected as an IEEE Micro Top Pick. |  |

| [12/2023] | Ruslan successfully defends his Ph.D. thesis! Congratulations! |  |

| [9/2023] | Rajit participated in a tutorial on open-source neuromorphic systems, including thte ACT toolflow for asynchronous design at ESSCIRC 2023. |  |

| [7/2023] | Rajit presented a tutorial on asynchronous design and the ACT toolflow at ASYNC 2023. |  |

| [7/2023] | Two of our papers recognized at ASYNC 2023! - Karthi's paper on Opportunistic Mutual Exclusion is a finalist for the best paper award!

- Our Timed Signaling Processes paper is selected as the best paper at the conference!

|  |

| [7/2023] | Rajit presented a tutorial on using the ACT asynchronous design flow at the Telluride Neuromorphic Cognition Engineering workshop. |  |

| [6/2023] | Congratulations to Prafull, heading to Brookhaven National Labs! |

| [6/2023] | Xiang successfully defends his Ph.D. thesis! Congratulations! Xiang is headed to Meta. |  |

| [6/2023] | Our latest ISCA paper with Prof. Bhattacharjee's group on brain-computer interfaces receives a best paper award! |  |

| [6/2023] | Our ISCA paper with Prof. Bhattacharjee's group on brain-computer interfaces selected for inclusion in the ISCA-50 retrospective. |  |

| [5/2023] | Rajit presented at an ISCAS tutorial on using Ising machines to solve combinatorial optimization problems. The tutorial was organized by Jaijeet Roychowdhury (Berkeley) and Sankar Basu (NSF), and included talks by Masanao Yamaoka (Hitachi), Hideo Mabuchi (Stanford), and Jaijeet Rowchowdhury. |

| [5/2023] | Four regular track papers from the group accepted to the IEEE ASYNC symposium!- Prafull's paper (with Johannes Leugering) is on an efficient bit-vector distributed data structure for neuromorphic applications.

- Karthi's paper (with Yoram Moses) is on a novel opportunistic mutual exclusion algorithm that uses zig-zag causality—the first use of timing zig-zags to improve performance.

- Xiang's paper is on a verification-driven approach to asynchronous design.

- We published our work with Prof. Yoram Moses (Technion) on the role of time in ordering events in a digital circuit. Our paper shows that zig-zags are sufficient as well as necessary for ordering actions in the timed asynchronous circuit setting.

|  |

| [4/2023] | Prafull successfully defends his Ph.D. thesis! Congratulations! Prafull is the final Cornell Ph.D. student from the group. |  |

| [4/2023] | Rajit gave an invited talk on the case for full-stack co-design for neuromorphic systems at the NICE 2023 workshop. |  |

| [3/2023] | Our group is participating in the DARPA program on Quantum-inspired Classical Computing (QUICC). The project is led by Prof. Roychowdhury from Berkeley, and includes Nokia and Yale. |

| [12/2022] | Karthi joins the group as a PhD student! |

| [11/2022] | Prafull's paper on a field-programmable encoding for AER accepted to Frontiers in Neuroscience! |

| [11/2022] | Our work on an open-source cell characterizer for asynchronous logic presented at WOSET. |

| [9/2022] | Mattia and Thomas join the group as Ph.D. students! |

| [8/2022] | Our work with Abhishek Bhattacharjee's group on brain-computer interfaces is presented at HotChips. |

| [7/2022] | Rajit gave a presentation on the use of asynchronous circuits in the design and implementation of large-scale neuromorphic systems at the annual Telluride neuromorphic cognition engineering workshop. |

| [6/2022] | Videos from the 2022 summer school on asynchronous design are now available. |

| [5/2022] | Congratulations to Rui, headed to Intel. |

| [2/2022] | Yihang successfully defends his Ph.D. thesis! Congratulations! Yihang is headed to Meta. |  |

| [12/2021] | Ruslan's paper on emulating asynchronous logic on synchronous FPGAs is accepted to IEEE TCAD. The paper presents a unified method for emulating a large number of asynchronous circuit families on clocked FPGA platforms. |

| [9/2021] | Rui successfully defends his Ph.D. thesis! Congratulations! He is the first Yale Ph.D. student to graduate from the AVLSI group. |  |

| [9/2021] | Wenmian and Yi-Shan's paper on static timing and power analysis for asynchronous logic wins the best paper award for ASYNC 2020! (Awarded at the 2021 conference as the 2020 conference was cancelled due to COVID. There was a two-way tie.) |

| [8/2021] | Rui's paper on asynchronous high-level synthesis is a finalist for best paper at ASYNC 2021! |

| [7/2021] | Prafull, Rui, Linc, and Yihang have regular track papers accepted to the 2021 ASYNC Symposium. Prafull's paper is on an improved AER circuit that performs well for a wide range of input scenarios. Rui, Linc, and Yihang's paper presents a high-level synthesis (HLS) engine for asynchronous circuits that outperforms a number of existing HLS tools (academic and commercial). |  |

| [7/2021] | Congratulations to Nabil, headed to Georgia Tech in 2022. |

| [5/2021] | Congratulations to Ioannis, headed to Blue Cheetah Analog Design. |

| [4/2021] | An overview of our group's project with UT Austin on an open-source EDA flow for asynchronous logic to appear in IEEE Design & Test. |

| [3/2021] | Congratulations to Samira, headed to Owl AI! |

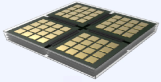

| [3/2021] | We just received our 12nm chips! |  |

| [1/2021] | Our ISCA paper with Prof. Bhattacharjee's group on balancing specialization with flexibility in architectures for brain-computer interfaces is selected as an IEEE Micro Top Pick. |  |

| [1/2021] | Congratulations to Ned, headed to Siden.io! |

| [10/2020] | Ned successfully defends his Ph.D. thesis! Congratulations! |  |

| [9/2020] | Updates to our open-source asynchronous VLSI tools will be presented at the WOSET 2020 workshop to be held in conjunction with ICCAD. This includes the current status of the flow, a power detailed router, and an approach to partitioning. |

| [8/2020] | We developed a dedicated hardware-based solution for Bluetooth-based contact tracing that is based on current public health guidelines for COVID-19. The solution preserves the privacy of participants until they come in contact with a known positive user, at which point the contact is revealed to public health officials to supplement their manual contact tracing efforts. Our approach balances individual privacy with the needs of public health officials and is more accurate than using phones. preprint |  |

| [7/2020] | Ned's paper on a unified approach to multiple arbitration problems accepted to IEEE Transactions on Circuits and Systems I: Regular Papers. |

| [7/2020] | Yihang's paper on a gridded cell placement flow accepted to ICCAD. |  |

| [7/2020] | Rajit to speak about system-level issues for neuromorphic computing systems at the DAC 2020 workshop on neuromorphic computing. |  |

| [7/2020] | Congyang Li joins the group as a Ph.D. student. |

| [6/2020] | Dr. Nabil Imam is visiting the group for a few months, after working with the TrueNorth team at IBM Research, and then the Loihi team at Intel Labs. Welcome back! |

| [6/2020] | Xiayuan Wen joins the group as a Ph.D student. |

| [6/2020] | Our project on design automation for asynchronous logic once again selected as one of the highlights at the DARPA ERI summit! |  |

| [4/2020] | Congratulations to Wenmian for successfuly defending his Ph.D. thesis! He will be joining Synopsys. |  |

| [3/2020] | Our paper with Prof. Bhattacharjee's group on a hardware architecture for brain-computer interfaces accepted to the 2020 International Symposium on Computer Architecture (ISCA). |  |

| [2/2020] | Samira and Wenmian have regular track papers accepted to the 2020 ASYNC Symposium. Wenmian's paper (with our collaborators at UT Austin) is the first complete static timing and power analysis engine for asynchronous circuits. It introduces the notions of arrival time, required time, and slack for asynchronous circuits, reports critical cycles, and is capable of handling circuits with millions of gates. Samira's paper shows how to reduce the staticizer overhead in asynchronous circuits through sharing. |  |

| [1/2020] | Rajit to speak about neuromorphic computing at the Technion. |

| [11/2019] | Rajit and Samira present an update on the state of our design automation tools for asynchronous circuits at the WOSET workshop at ICCAD. |

| [10/2019] | Rajit presents an overview of our project on hardware verification at the New England Systems Verification Day, hosted by MIT. |

| [8/2019] | Rajit to speak about neuromorphic computing at the DOE Workshop on Modeling and Simulation of Systems and Applications. |

| [7/2019] | Ned's paper on adaptive digit-serial addition accepted to IEEE Transactions on VLSI. |

| [6/2019] | Our project on design automation for asynchronous logic selected as one of the highlight posters at the DARPA ERI summit! |  |

| [6/2019] | Rajit to give an invited talk on neuromorphic computing at the 2019 New York Scientific Data Summit. |

| [5/2019] | Samira's paper on an asynchronous memory compiler nominated for best paper at ASYNC 2019! |

| [3/2019] | Yi-Shan Lu (Prof. Pingali's group at UT Austin) and Wenmian Hua's submission to the TAU 2019 gate sizing and buffer insertion contest was selected as one of the top entries! |

| [2/2019] | Our asynchronous circuit design tools are available on GitHub! |

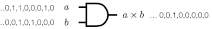

| [1/2019] | Our paper with Yoram Moses on a new framework called asynchronous signalling processes accepted for publication to ASYNC 2019. The paper shows that the limitations to delay-insensitive computation are a result of the single output assumption, and that two outputs are sufficient to implement arbitrary functions with delay-insensitive circuits. |  |

| [1/2019] | Samira's paper on an asynchronous memory compiler accepted for publication to ASYNC 2019. The compiler can generate multi-banked pipelined asynchronous memories that support read-modify-write operations. |  |

| [1/2019] | Ioannis Karageorgos joins the group as a postdoctoral scholar. Welcome! |

| [11/2018] | Our paper with Stanford and University of Waterloo on a new mixed-signal neuromorphic chip accepted to the Proceedings of the IEEE. |  |

| [11/2018] | Nitish's paper on operation-dependent desynchronization accepted to IEEE Transactions on VLSI. |  |

| [10/2018] | Our joint project on developing parallel EDA tools for asynchronous VLSI with UT Austin (Prof. Pingali's group) and Texas State (Prof. Burtscher's group) will be presented at the first Workshop on Open-Source EDA Tools held at ICCAD. |

| [9/2018] | Saber's paper on the impact of communication cost on the design of neuromorphic systems accepted to a special issue of the Journal of Physics D. |

| [9/2018] | Ned's paper on better constant-response time counters accepted to IEEE Transactions on VLSI. |  |

| [8/2018] | Ruslan Dashkin and Xiang Wu join the group as Ph.D. students. |

| [8/2018] | Rajit presents an overview of asynchronous circuit design automation at the IEEE Circuits and Systems Society Seasonal School on Logic Synthesis, Porto Alegre, Brazil hosted by UFRGS. |  |

| [7/2018] | Saber Moradi will be heading to silicon valley to work on machine learning hardware. Congratulations! |

| [7/2018] | Rui Li joins the group as a Ph.D. student. |

| [5/2018] | Rajit presents an overview of asynchronous design at Yale's annual science and engineering forum. |

| [4/2018] | The group, along with collaborators at UT Austin, Texas State, and Sandia National Labs selected for multiple DARPA efforts as part of the Electronics Resurgence Initiative. |

| [3/2018] | Lab alum Jon Tse demonstrating Intel's Loihi neuromorphic chip! |

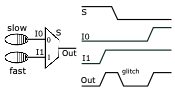

| [1/2018] | Wenmian's paper on timing analysis for asynchronous circuits appears in IEEE TCAD. The paper studies the case of AND-causal asynchronous circuits, and shows that such circuits are not only approximately periodic, but in fact are exactly periodic. More importantly, our analysis relaxes the constraint that the underlying circuit is strongly connected, a requirement for previous related work. We show how the theory can be used to create a metastability-free interface between asynchronous and synchronous logic. |

| [11/2017] | Yihang Yang joins the group as a Ph.D. student. He is the first Yale Ph.D. student to join the group. |

| [7/2017] | Zhan Liu joins the group as a co-advised Ph.D. student with Prof. Ma serving has his primary advisor. |

| [7/2017] | Rajit is elected to Yale's faculty senate for the faculty of arts and sciences. |

| [6/2017] | The group's new lab space is ready! |  |

| [2/2017] | Our paper with Yoram Moses on characterizing delay-insensitivity in asynchronous circuits is accepted to ASYNC 2017. The paper provides a rigorous mathematical justification for the observation that delay-insensitive circuits with single output gates are extremely limited. |  |

| [8/2016] | The TrueNorth chip is now in the Computer History Museum! |

| [8/2016] | The group will be moving to Yale in January 2017! |  |

| [8/2016] | The TrueNorth project wins the inaugural Misha Mahowald Prize for neuromorphic engineering! The citation reads: "For the development of TrueNorth, a neuromorphic CMOS chip that simulates 1 million spiking neurons with connectivity and dynamics that can be flexibly programmed while consuming only 70 milliwatts. This scalable architecture sets a new standard and brings us closer to achieving the high levels of performance in brains." |

| [6/2016] | Rajit selected by Cornell Tech students as a "Professor of the Year" for contributions to teaching. |

| [3/2016] | Our Science paper with IBM was selected for the 2014 Pat Goldberg Math/CS/EE Best Paper award (first place) by IBM Research. |

| [2/2016] | Sandra's paper on gradual synchronization accepted to ASYNC 2016. |  |

| [1/2016] | Our paper on comparing stochastic and deterministic computing selected as one of the "Best of Computer Architecture Letters" for 2015. It will be presented at a special session at HPCA in March. |  |

| [12/2015] | Benjamin Hill returns to successfully defend his Ph.D. thesis. Ben has been on the Olin faculty since January. |  |

| [12/2015] | Julia Karl successfully defends her M.S. thesis. |  |

| [10/2015] | Robert Karmazin successfully defends his Ph.D. thesis. Rob will be joining Intel. |  |

| [9/2015] | Our invited paper with IBM on the TrueNorth design to appear in IEEE Transactions on Computer Aided Design in October. |

| [9/2015] | Jon Tse successfully defends his Ph.D. thesis. Jon will be joining Intel. |  |

| [6/2015] | Sean Ogden joins the group as a Ph.D. student. |

| [6/2015] | Wenmian Hua and Nitish Srivastava join the group as Ph.D. students. |

| [5/2015] | Project web page for our neuromorphic chip/software project with Stanford and U. Waterloo is now up! |  |

| [3/2015] | Rajit's paper on comparing stochastic computing approaches to conventional digital computing accepted to IEEE CAL. |  |

| [2/2015] | Stephen successfully defended his Ph.D. thesis on asynchronous circuit verification. Stephen will be joining Google. |  |

| [2/2015] | Three regular papers from the group accepted to the Asynchronous Circuits Symposium (ASYNC) to be held May 2015. Students Robert Karmazin, Carlos Otero, Stephen Longfield, and Jonathan Tse contributed to two papers on timing-driven placement and hardware-software trade-offs in a low power AES implementation. A third paper on a formal proof of the nature of the isochronic fork timing assumption is a collaboration with Prof. Yoram Moses from the Technion. This represents 16% of the accepted full papers. |  |

| [2/2015] | Stephen's paper on using type systems to prevent errors in high-level self-timed circuit descriptions (a collaboration with Ross Tate's group in CS) accepted for publication at PLDI 2015. |  |

| [2/2015] | Rajit is

named a Stephen H. Weiss Presidential Fellow, in recognition of his contributions to undergraduate education at Cornell. |

| [1/2015] | Rajit is appointed the Associate Dean for Research at Cornell Tech. |  |

| [1/2015] | Benjamin Hill joins the Olin faculty. |  |

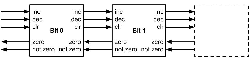

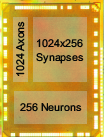

| [8/2014] | Our paper with IBM research on TrueNorth, a single chip million neuron system is published in Science, and made the cover! Additional coverage in the media: IBM press release, DARPA press release, NY Times, Wall Street Journal, Wired, Scientific American, Reuters, MIT Technology Review, Cornell Chronicle. This project was made possible thanks to support via the DARPA SyNAPSE program.

Highlights: First single chip million neuron neuromorphic architecture. Fully digital, deterministic, highly programmable neurons, synapses, and communication with a glueless chip-to-chip network and less than 70mW power. Hybrid QDI and bundled data asynchronous design, with a low frequency clock for 1:1 correspondence to a parallel discrete event software model. 4096 cores and 5.4B transistors. |  |

| [8/2014] | Our paper with IBM research on TrueNorth's efficiency and scalability titled Real-Time Scalable Cortical Computing at 46 Giga-Synaptic OPS/Watt with ~100x Speedup in Time-to-Solution and ~100,000x Reduction in Energy-to-Solution is accepted for publication to Supercomputing 2014. The paper is an ACM Gordon Bell Prize finalist. |  |

| [7/2014] | Carlos Otero successfully defended his Ph.D. thesis on asynchronous circuits for ubiquitous computing. |  |

| [7/2014] | Sandra Jackson successfully defended her Ph.D. thesis on synchronization techniques. |  |

| [6/2014] | Stephen Longfield's paper on concurrency reduction for fast verification accepted for publication at ICCAD 2014. |  |

| [3/2014] | Nabil successfully defends his Ph.D. thesis on neuromorphic computing. Nabil is joining IBM Research. |  |

| [2/2014] | Our paper with François Guimbretière's group on a new low power e-book reader implementation using a hybrid processor-microcontroller appears in ACM TECS. |  |

| [2/2014] | Ben Tang's paper on using NEM relays to implement asynchronous logic accepted for publication at ASYNC 2014. |  |

| [1/2014] | Our paper with François Guimbretière's group on using heterogenous multicore processors for low power user interface implementation accepted to CHI 2014. |  |

| [12/2013] | Carlos Otero's paper titled ULSNAP: An Ultra-low Power Event-Driven Microcontroller for Sensor Network Nodes accepted for publication at ISQED 2014. |  |

| [12/2013] | Ben Tang successfully defends his Ph.D. thesis. |  |

| [11/2013] | Nature story on our new ONR-supported neuromorphic chip project, a collaboration between Stanford, U. Waterloo, and our group. |  |

| [8/2013] | Nabil quoted in Technology Review article about our neuromorphic architecture project. |

| [8/2013] | IBM press release describes the programming interface for the neuromorphic hardware being developed for the SyNAPSE project. |

| [7/2013] | Rajit Manohar's appointment is now 100% at Cornell Tech. |  |

| [6/2013] | Edward Bingham joins the group as a Ph.D. student. Ned starts his graduate work at Cornell Tech. |

| [5/2013] | Stephen Longfield's paper titled "Inverting Martin Synthesis for Verification" selected as the best paper at ASYNC 2013. |  |

| [3/2013] | Students Benjamin Hill, Julia Karl, Rob Karmazin, Stephen Longfield, Carlos Otero, and Jonathan Tse contributed to five papers accepted to the Asynchronous Circuits Symposium (ASYNC) in Santa Monica, CA this May. Three papers from the group address topics including the verification of asynchronous circuits, physical design automation, and an on-chip link study. Two other papers were led by Intel and Raytheon. |  |

| [2/2013] | Nabil Imam receives an IBM Ph.D. fellowship. |

| [1/2013] | Julia Karl joins the group as a Ph.D. student. Julia starts her graduate work at Cornell Tech. |

| [11/2012] | Rajit Manohar appointed Associate Dean for Academic Affairs at the newly created Cornell Tech campus. |  |

| [9/2012] | Benjamin Tang wins the best presentation award in his session at the ION GNSS Technical Meeting. Ben presented his work on examining accuracy and power tradeoffs in the design of a GPS baseband processor. |  |

| [9/2012] | Rajit receives the 2012 Kenneth A. Goldman '71 Excellence in Teaching award from the College of Engineering. |

| [7/2012] | Rajit Manohar joins the newly created Cornell Tech faculty. |  |

| [5/2012] | Carlos succesfully defends his M.S. thesis on static power reduction techniques. |  |

| [5/2012] | Our paper with IBM Research titled "A Digital Neurosynaptic Core Using Event-Driven QDI Circuits" (presented by Nabil) selected as the best paper at ASYNC 2012. |  |

| [2/2012] | Three papers from the group will be presented at the Asynchronous Circuits Symposium (ASYNC) in Denmark this May. The topics they address include neuromorphic systems, energy-efficient floating-point arithmetic, and low power GPS. |  |

| [12/2011] | Creating artificial intelligence based on the real thing. New York Times, 12/5/2011. |

| [8/2011] | Our work with IBM research on developing a neuromorphic chip receives significant press coverage (IBM announcement, Associated Press, Bloomberg, CNET, EE Times, Nature News, NY times, PC Magazine, PC World, Technology Review, VentureBeat, WSJ, Xinhua, ZDNet, many others). Our CICC paper on the topic will appear in September 2011. This effort is funded by the DARPA SyNAPSE program. |  |

| [8/2011] | Basit Riaz Sheikh successfully defends his Ph.D. thesis on asynchronous floating-point arithmetic. |  |

| [8/2011] | Along with Prof. Tsuhan Chen's group, we have been selected as members of the newly formed Intel Science and Technology Center on Embedded Computing. |

| [5/2011] | Filipp and Basit participate in the 2011 graduation ceremonies! |  |

| [3/2011] | Filipp Akopyan successfully defends his Ph.D. thesis on hybrid synchronous-asynchronous design. Filipp is joining IBM research. |  |

| [2/2011] | Cornell is hosting ASYNC 2011 this April. |  |

| [1/2011] | Nabil Imam's paper on AER circuits for neuromorphic systems accepted for publication at ASYNC 2011. |

| [7/2010] | Rajit Manohar appointed Associate Dean for Research and Graduate Studies in the College of Engineering. |  |

| [6/2010] | Rajit Manohar promoted to full Professor. |

| [5/2010] | Basit Riaz Sheikh's paper on energy-efficient floating-point addition titled "An Operand Optimized Asynchronous IEEE 754 Double Precision Floating-point Adder" selected as the best paper at ASYNC 2010. |

| [4/2010] | Stephen Longfield receives an NSF Graduate Fellowship and Jonathan Tse receives an honorable mention. |  |

| [3/2010] | Two ASYNC papers from the group nominated for the best paper award by the selection committee: Basit's paper on energy-efficient floating-point addition, and Chris' paper on using two-phase routing in an asynchronous FPGA architecture. |

| [2/2010] | Three papers from the group will be presented at the Asynchronous Circuits Symposium (ASYNC) in Grenoble this May. The topics they address are leakage management in asynchronous circuits, energy-efficient floating-point arithmetic, and reducing routing power in an asynchronous FPGA. |  |

| [1/2010] | Rajit Manohar appointed interim Associate Dean for Research and Graduate Studies in the College of Engineering. |  |

| [12/2009] | Chris LaFrieda successfully defends his Ph.D. thesis on relaxed QDI circuits. Chris is joining Achronix Semiconductor. |  |

| [11/2009] | Achronix Semiconductor, a startup based on research from the AVLSI group, is honored with the IET innovations award for startup of the year. Achronix' technology is based on John Teifel's Ph.D. thesis (2004), and papers from 2004 and earlier. |

| [9/2009] | The IBM team (with us as members) for the DARPA SyNAPSE program is renewed for Phase 1. |  |

| [5/2009] | Rajit Manohar selected for the Ruth and Joel Spira Teaching award. |

| [5/2009] | Abin Thomas' M.Eng. project selected as one of the best M.Eng. projects this year. |

| [9/2008] | IBM announces their efforts to develop a cognitive computer. Our group is participating in this effort in collaboration with IBM. |  |

| [5/2008] | David Fang successfully defends his Ph.D. thesis on profiling asynchronous circuits. David is joining Achronix Semiconductor. |  |

| [4/2008] | 3D thermal characterization chip functional. Our CICC paper describing the characterization results will appear in September. |  |

| [2/2008] | NASA test chip functional over the required temperature range (77K to 400K). |  |

| [9/2007] | The paper "Enabling Cognitive Architectures for UAV Mission Planning" summarizing the work done for the DARPA ACIP program by the Lockheed Martin-led team that included Cornell selected for the paper award at HPEC. |

| [9/2006] | Rajit Manohar attends NAE's Frontiers of Engineering Symposium. |  |

| [9/2006] | David Biermann successfully defends his Ph.D. thesis on an adaptive voltage scaling architecture. Dave will join Intel. |  |

| [8/2006] | Song Peng successfully defends his Ph.D. thesis on fault-tolerant asynchronous logic. Song will join Cadence. |  |

| [7/2006] | We are now part of the next three years of the FCRP C2S2 center. |  |

| [3/2006] | Filipp's paper "A Level-crossing Flash Asynchronous Analog-to-Digital Converter" selected as the best paper at ASYNC 2006. |

| [10/2005] | The paper "Dense sensor networks are also energy efficient: when 'more' is 'less'" by Yao-Win Hong, Birsen Sirkeci-Mergen and Profs. Scaglione and Manohar wins the Ellersick Award for best unclassified paper at MILCOM'05. |

| [9/2005] | EE times story on a startup based on work from our lab. |

| [9/2005] | Rajit Manohar named to MIT Technology Review Magazine's TR35. |  |

| [9/2005] | Testing SNAP complete! The processor operates correctly on first silicon. C programs run succesfully on the test board. |  |

| [7/2005] | Chris LaFrieda successfully defends his M.S. thesis. |  |

| [7/2005] | Filipp Akopyan successfully defends his M.S. thesis. |  |

| [4/2005] | Clint Kelly and Virantha Ekanayake successfully defend their Ph.D. theses. Clint and Virantha are co-founders of Achronix Semiconductor, along with Rajit. |  |

| [3/2005] | We are part of TRUST, the newly formed NSF center on Cybersecurity. |  |

| [3/2005] | Virantha Ekanayake will join Johns Hopkins University as an Assistant Professor in the Fall. |

| [5/2004] | John Teifel successfully defends his Ph.D. thesis, providing an existence proof that it is possible to graduate from the AVLSI group! John will join Sandia National Labs. |  |