Asynchronous Field-Programmable Gate Arrays (AFPGAs)

|

|

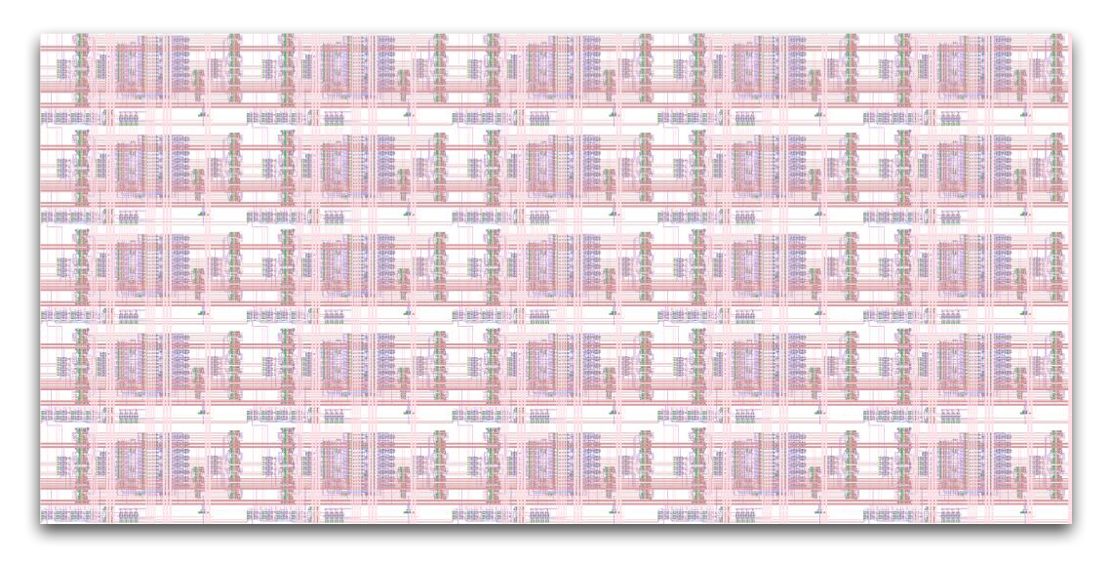

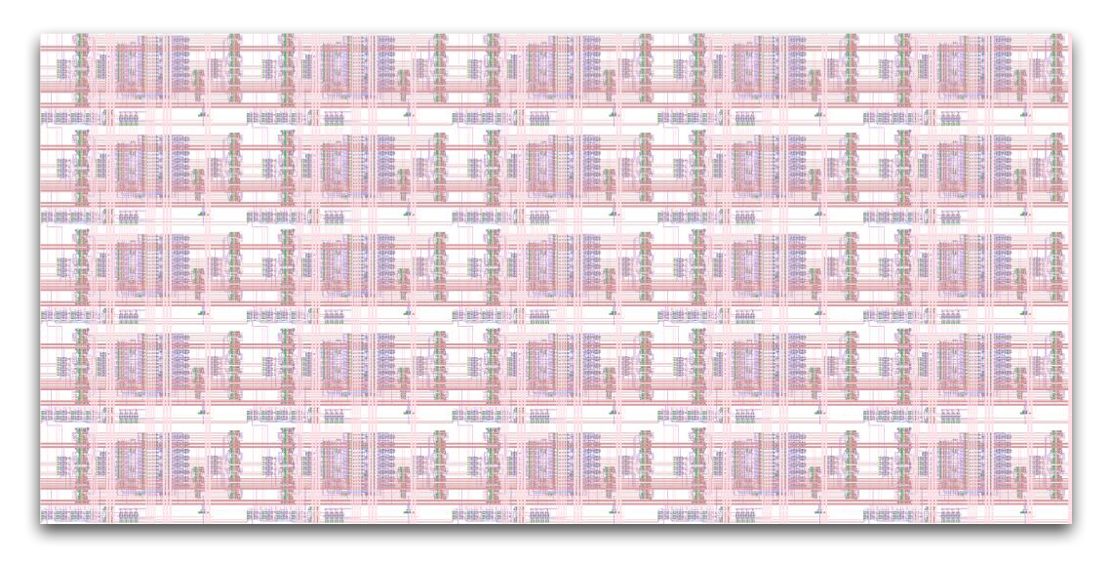

| Asynchronous FPGA |

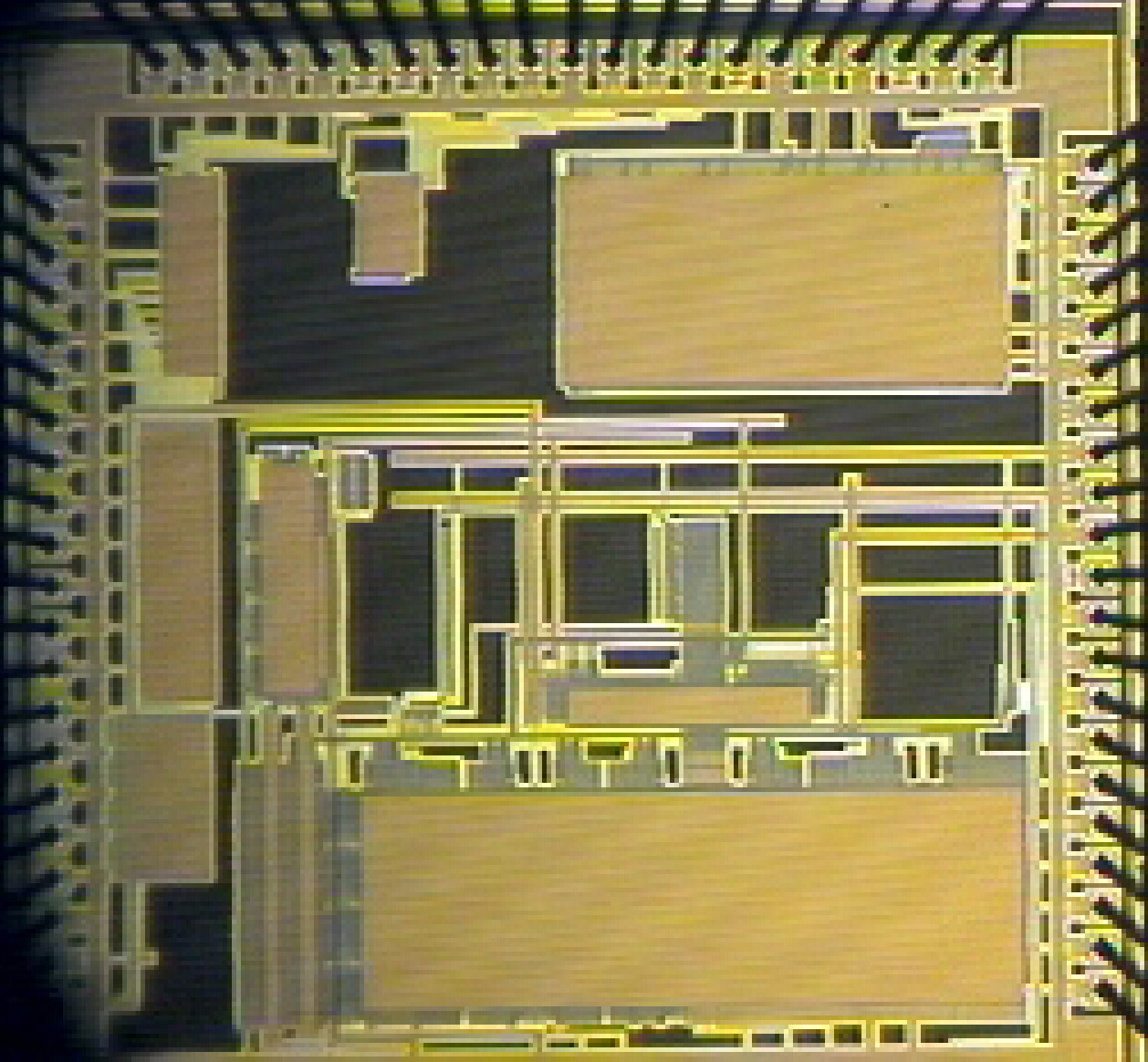

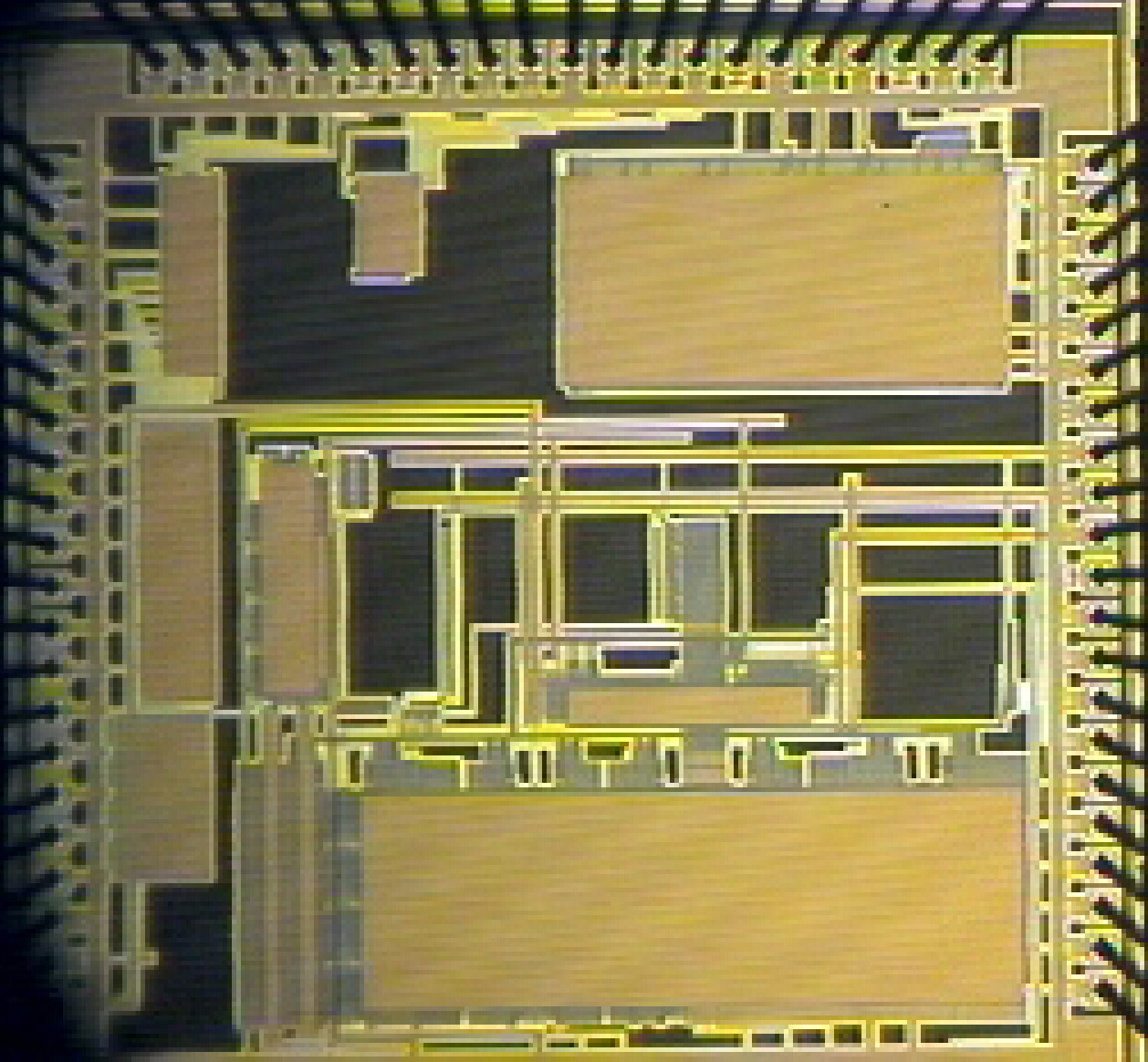

Test chip |

| |

|

| Raspberry Pi with a recent AFPGA test board |

Efficient pipelining support is important for FPGAs to attain high

performance. We have developed two asynchronous FPGA architectures

that have integrated pipelining support and that are configurable at

the pipeline-stage level. A designer using these FPGAs need only think

of the computation in terms of its dataflow graph, and need not be

concerned with the detailed asynchronous circuit implementation.

These coarse-grain asynchronous FPGAs do not need explicit retiming

registers to support pipelining, since our asynchronous FPGA has the

property of slack

elasticity. The net result is an efficient, high-performance

FPGA architecture that is (for the first time) competitive with custom

asynchronous logic.

Our design supports the use of standard clocked place-and-route tools,

and we have also developed a logic synthesis method for automatically

mapping asynchronous designs to our architecture.

We are also exploring the impact of 3D integration on the design

of asynchronous FPGA architectures.

- Participants

- Thomas Jagielski

- Alums

- Ruslan Dashkin (Ph.D. 2024)

- David Fang (Ph.D. 2008)

- Benjamin Hill (Ph.D. 2015)

- Robert Karmazin (Ph.D. 2015)

- Rui Li (Ph.D. 2021)

- Song Peng (Ph.D. 2006)

- John Teifel (Ph.D. 2004)

- Publications

- Prafull Purohit and Rajit Manohar.

Field-programmable encoding for address-event representation.

Frontiers in Neuroscience, 16, December 2022.

(pdf)

- Rashid Kaleem, Rajit Manohar, and Keshav Pingali.

Dionysus: CPUs as accelerators for FPGAs.

Work-in-progress session, Design Automation Conference (DAC), June 2017.

- Carlos Tadeo Ortega Otero, Jonathan Tse, Robert Karmazin, Benjamin Hill, and Rajit Manohar.

Automatic Obfuscated Cell Layout for Trusted Split-Foundry Design.

IEEE International Symposium on Hardware-Oriented Security and Trust, May 2015.

- Benjamin Hill, Robert Karmazin, Carlos Tadeo Ortega Otero, Jonathan Tse, and Rajit Manohar.

A Split-Foundry Asynchronous FPGA.

Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), September 2013.

(abstract, pdf)

- Christopher LaFrieda, Benjamin Hill, and Rajit Manohar.

An Asynchronous FPGA with Two-Phase Enable-Scaled Routing.

Proceedings of the 16th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2010.

(abstract, pdf) — Best paper nominee

- S. Ramaswamy, L. Rockett, D. Patel, S. Danziger, R. Manohar, C. Kelly, J. Holt, V. Ekanayake, D. Elftmann.

A Radiation Hardened Reconfigurable FPGA.

Proceedings of the IEEE Aerospace Conference, March 2009.

(abstract, pdf)

- Rajit Manohar, Clinton Kelly IV, et al.

Development of Reprogrammable Low Power High Density High Speed RADHARD FPGAs.

Government Microcircuit Applications and Critical Technology Conference, March 2007.

- Rajit Manohar.

Reconfigurable Asynchronous Logic.

Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), September 2006.

(abstract, pdf)

- David Fang, Christopher LaFrieda, Song Peng, and Rajit Manohar.

A 3-Tier Asynchronous FPGA.

Proceedings of the 23rd International VLSI/ULSI Multilevel Interconnection Conference (VMIC), September 2006.

(abstract, pdf)

- Rajit Manohar, Clinton Kelly IV, J. Holt, Chris Liu, Leonard Rockett, Dinu Patel, Steven Danzinger.

Application of Low Power High Density Gigahertz Speed Commercial FPGA Technology to High Radiation Applications using RADHARD-by-Process Techniques.

Proceedings of the 9th Military and Aerospace Programmable Logic Devices International Conference, September 2006.

- David Fang, John Teifel, and Rajit Manohar.

A High-Performance Asynchronous FPGA: Test Results.

2005 IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM), April 2005.

(abstract, pdf)

- Song Peng, David Fang, John Teifel, and Rajit Manohar.

Automated Synthesis for Asynchronous FPGAs.

13th ACM International Symposium on Field Programmable Gate Arrays (FPGA), February 2005.

(abstract, pdf, ps)

- John Teifel and Rajit Manohar.

An Asynchronous Dataflow FPGA Architecture.

IEEE Transactions on Computers (special issue on field-programmable logic), November 2004.

(abstract, pdf)

- John Teifel and Rajit Manohar.

Static Tokens: Using Dataflow to Automate Concurrent Pipeline Synthesis.

Proceedings of the 10th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), April 2004.

(abstract, pdf, ps)

- John Teifel and Rajit Manohar.

Highly Pipelined Asynchronous FPGAs.

12th ACM International Symposium on Field-Programmable Gate Arrays (FPGA), Monterey, CA, February 2004. [Please see abstract].

(abstract, pdf, ps)

- John Teifel and Rajit Manohar.

Programmable Asynchronous Pipeline Arrays.

Proceedings of the 13th International Conference on Field Programmable Logic and Applications (FPL), pp. 345--354, Lisbon, Portugal, September 2003.

(abstract, pdf, ps)

|